Implementing error correction in a quantum computer requires putting together a lot of different things. Of course, you want to start with good physical qubits that have as low a physical error rate that you can achieve. You want to add in an error correction algorithm, like the surface code, color code, q-LDPC, or others that can be implemented in your architecture, and you need a fast real time error decoder that can look at the circuit output and very quickly determine what the error is so it can be corrected. The error decoder portion doesn’t get as much attention in the media as the other things, but it is a very critical portion of the solution. Riverlane is concentrating on providing products for this with a series of solutions they name Deltaflow which consists of both a classical ASIC chip along with software. The Deltaflow solution consists of a powerful error decoding layer for identifying errors and sending back corrective instructions, a universal interface that communicates with the computer;s control system, and a orchestration layer for coordinating activities.

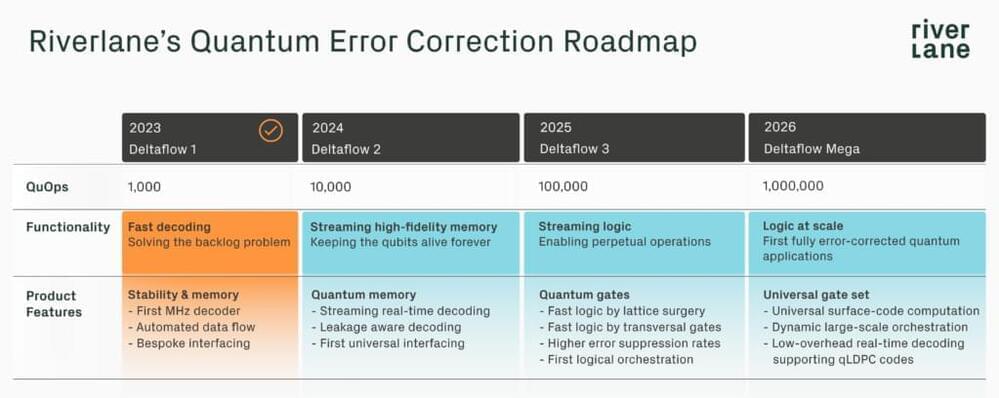

Riverlane has released its Deltaflow Error Correction Stack Roadmap that show yearly updates to the technology to support an increase in the number of QuOps (error free Quantum Operations) by 10X every year. We reported last year on a chip called DD1 that is part of their Deltaflow 1 solution that is capable of supporting 1,000 QuOps using a surface code error correction algorithm. And now, Riverlane is defining solutions that will achieve 10,000 QuOps with Deltaflow 2 later this year, 100,000 QuOps with Deltaflow 3 in 2025, and 1,000,000 QuOps, also called MegaQuops in 2026, with their Deltaflow Mega solution.

One characteristic that Riverlane is emphasizing in these designs is to perform the decoding in real time in order to keep the latencies low. Although it is fine for an academic paper to send the ancilla data off to a classical computer and have it determine the error, it might take milliseconds for the operation to complete. That won’t cut it in a production environment running real jobs. With their Deltaflow chips, these operations can be performed at megahertz rates and Riverlane has implemented techniques such as a streaming, sliding window, and parallized decoding approaches to increase the throughput of the decoder chips as much as possible. In future chips they will be implementing “fast logic” capabilities for Clifford gates using approaches including lattice surgery and transversal CZ gates.

Leave a reply