May 11, 2024

New “Iontronic Memristor” Could Revolutionize Brain-Like Computing Using Only Salt and Water

Posted by Dan Breeden in category: computing

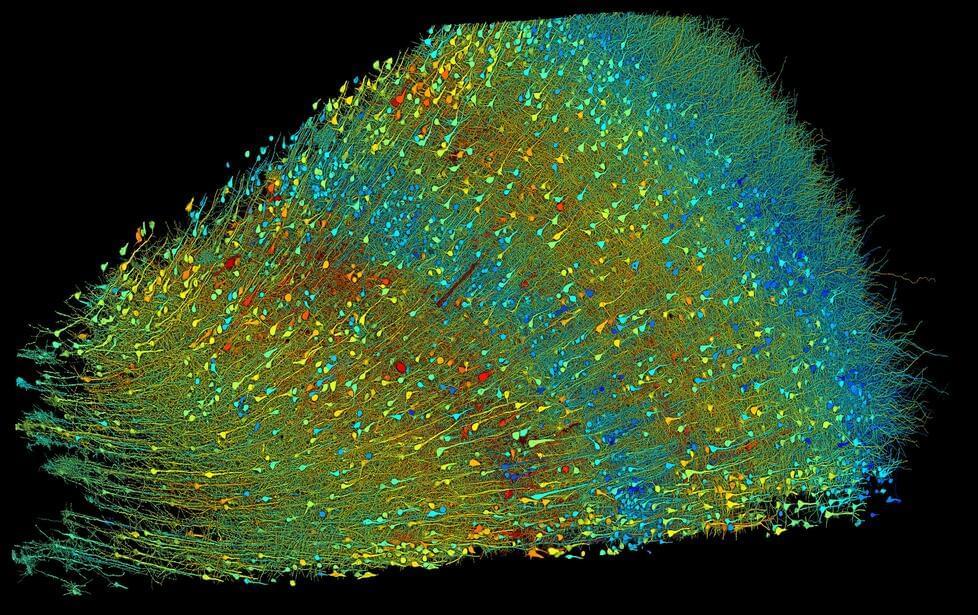

Researchers say this novel device, barely larger than a human hair, functions as an artificial synapse, mimicking the brain’s unique ability to process and share information.

“The brain’s computing principles (neurons connected by synapses) and information carriers (ions in water) both differ fundamentally from those of conventional computers,” researchers wrote. “Building on this distinction, we present an aqueous memristor that emulates the brain’s short-term synaptic plasticity features through ion transport in water, mirroring the natural processes in the brain.”

In their findings, recently published in the Proceedings of the National Academy of Sciences, researchers highlighted that the iontronic memristor marks a significant departure from earlier models designed to mimic the brain’s communication pathways. Moreover, the device uniquely emulates the dynamic processes of human synapses in real time, using only salt and water to closely replicate how neurons transmit information naturally.